# EE109: Introduction to Embedded Systems Fall 2020 - Final Exam 11/21/20, 2PM - 3:40PM + 20 min to upload

[Complete all the information in the box below.]

|     | <no need<="" th=""><th>d to Fill this ou</th><th>t due to Grades</th><th>cope&gt;</th></no> | d to Fill this ou  | t due to Grades       | cope>             |

|-----|---------------------------------------------------------------------------------------------|--------------------|-----------------------|-------------------|

| Naı | me:                                                                                         |                    |                       |                   |

| Stu | dent ID:                                                                                    |                    |                       |                   |

| Em  | ail:                                                                                        | @usc.              | edu                   |                   |

| Le  | cture section (                                                                             | Circle One):       |                       |                   |

|     | Annavaram                                                                                   | Redekopp           | Weber                 | Weber             |

|     | <del>9 a.m.</del>                                                                           | <del>11 a.m.</del> | <del>12:30 p.m.</del> | <del>2 р.т.</del> |

|     |                                                                                             |                    |                       |                   |

# Calculators ARE allowed.

| Page | Ques. | Your score  | Max score | Recommended<br>Time |

|------|-------|-------------|-----------|---------------------|

| 1    |       |             | 0         | 0 min.              |

| 2    | 1     |             | 14        | 10 min.             |

| 3    | 2     |             | 15        | 15 min.             |

| 4    | 3     |             | 10        | 10 min.             |

| 5    | 4     |             | 12        | 15 min.             |

| 6    | 5     |             | 10        | 15 min.             |

| 7    | 6     |             | 12        | 20 min.             |

| 8    | 7     |             | 10        | 15 min.             |

|      | Total |             | 83        | 100 min.            |

|      |       | Scan/Upload |           | 20 min.             |

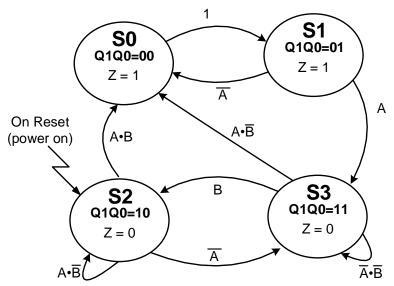

1. **State Machines I (14 pts.)**: Consider the **completed** state diagram shown below to answer the questions below.

a.) Complete the state transition table by filling in the next state columns and the output column in the table below.

| Currer | nt State |           | Next      | State    |          | Output |

|--------|----------|-----------|-----------|----------|----------|--------|

|        |          | A B = 0 0 | A B = 0 1 | A B = 10 | A B = 11 |        |

| State  | Q1 Q0    | State*    | State*    | State*   | State*   | Z      |

| S0     | 0 0      | S         | S         | S        | S        |        |

| S1     | 0 1      | S         | S         | S        | S        |        |

| S2     | 1 0      | S         | S         | S        | S        |        |

| S3     | 1 1      | S         | S         | S        | S        |        |

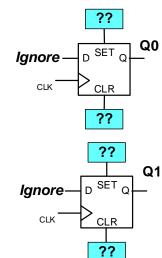

- b.) To implement the reset condition, what should be connected to the following flip flop inputs?

- i.) The **SET of the Q0 flip-flop** should be connected to:

- a. RESET

- b. not RESET

- c. 0 (GND)

- d. 1 (Vdd)

- ii.) The CLR of the Q0 flip-flop should be connected to:

- a. RESET

- b. not RESET

- c. 0 (GND)

- d. 1 (Vdd)

- iii.) The **SET of the Q1 flip-flop** should be connected to:

- a. RESET

- b. not RESET

- c. 0 (GND)

- d. 1 (Vdd)

- iv.) The CLR of the Q1 flip-flop should be connected to:

- a. RESET

- b. not RESET

- c. 0 (GND)

- d. 1 (Vdd)

RESET

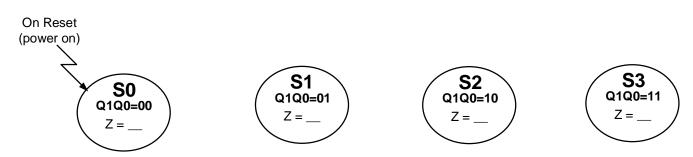

2. **State Machines II (15 pts).** Given the state transition table below, answer the following questions:

| Current | State |        | Next St | ate    |        | Output |

|---------|-------|--------|---------|--------|--------|--------|

|         |       |        | X=0     |        | K=1    |        |

| State   | Q1Q0  | State* | Q1*Q0*  | State* | Q1*Q0* | Z      |

| S0      | 0 0   | S2     | 1 0     | S1     | 0 1    | 1      |

| S1      | 0 1   | S1     | 0 1     | S0     | 0 0    | 1      |

| S2      | 1 0   | S3     | 1 1     | S3     | 1 1    | 0      |

| S3      | 1 1   | S2     | 1 0     | S1     | 0 1    | 0      |

a.) Use the state table above to complete the corresponding state diagram (*fill in/draw all the correct state transitions* and be sure to label them correctly based on the table). Combine transition arrows where appropriate. *Fill in the Z output values* for each state.

b.) Find a minimal, SOP equation for D1 (input to the Q1 flip-flop) and a minimal equation (SOP or POS) for Z. Show work and put your final answer in the blanks below.

$D_1 =$ \_\_\_\_\_

Z = \_\_\_\_\_

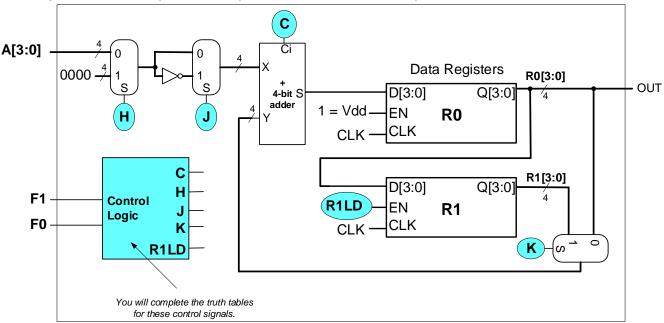

3. **Datapath Design I (10 pts.):** Consider the datapath below with the accompanying table showing the correspondence of **desired operations** to the function select bits, F[1:0]. Complete the table for the control signals: H, J, C, K, and R1LD to achieve the desired operations. All input and output numbers are 2's complement numbers.

Complete the table for the values of H, J, C, K and R1LD. Use d for don't care where appropriate.

| <b>Desired Operation</b>      | F1 | F0 | Н | J | С | K | R1LD |

|-------------------------------|----|----|---|---|---|---|------|

| R0 = R0 - A<br>R1 (no change) | 0  | 0  |   |   |   |   |      |

| R0 = R0 + 1<br>R1 (no change) | 0  | 1  |   |   |   |   |      |

| R0 = R1 - 1<br>R1 (no change) | 1  | 0  |   |   |   |   |      |

| Swap R0 and R1 values         | 1  | 1  |   |   |   |   |      |

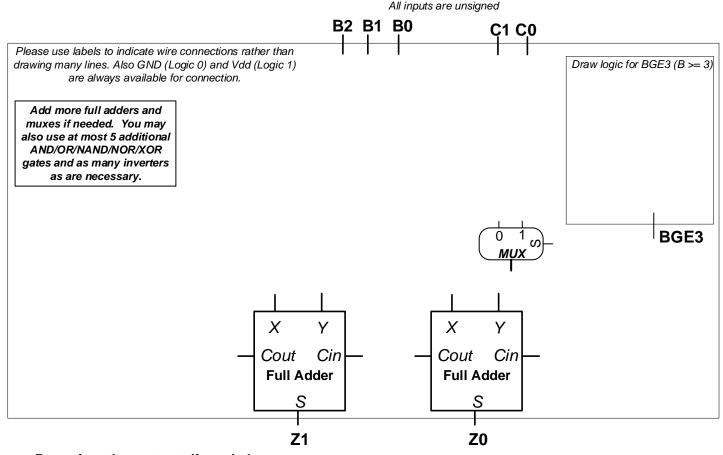

4. **Datapath Design II (12 pts.)**: Complete the combinational design below which takes in a 3-bit **unsigned** number, **B (B[2:0])** and 2-bit **unsigned** number **C (C[1:0])**. Your circuit should produce an **unsigned** output, Z (of appropriate number of bits) according to the description:

if (B >= 3) then

$$Z = B - C$$

else  $Z = B + 2_{10}$

You may draw additional full adders and/or 2-to-1 muxes if needed. You may use as many inverters as needed and may also use 5 additional simple AND/OR/NAND/NOR/XOR/XNOR gates.

- a.) What is the decimal range of values that may be output for Z: \_\_\_\_\_ to \_\_\_\_\_

- b.) How many bits are required to represent that range: \_\_\_\_\_

- c.) Complete the logic for the signal BGE3 (i.e. the condition  $B \ge 3$ ) in the box on the right.

- d.) Complete the rest of the circuit. Please label inputs with signal names rather than drawing long lines/wires.

Room for other outputs if needed

The output is also an unsigned number

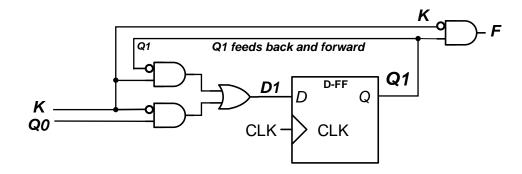

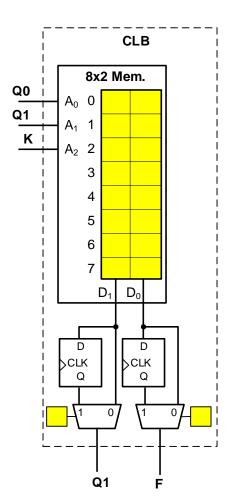

5. **FPGAs/Memories Design (10 pts.)**: Given the desired hardware design below complete the following question.

Show how to implement the design above using **one** 3-input, 2-output CLB by determining the contents of the 8x2 memory and the mux selects. Place a dash ('-') in any memory cell (bit place) that is a don't care.

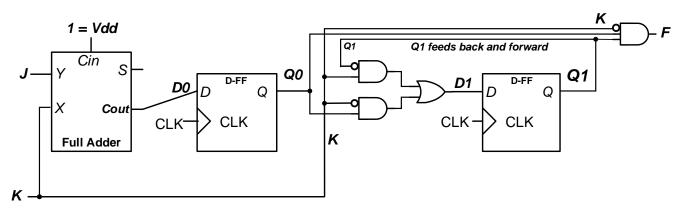

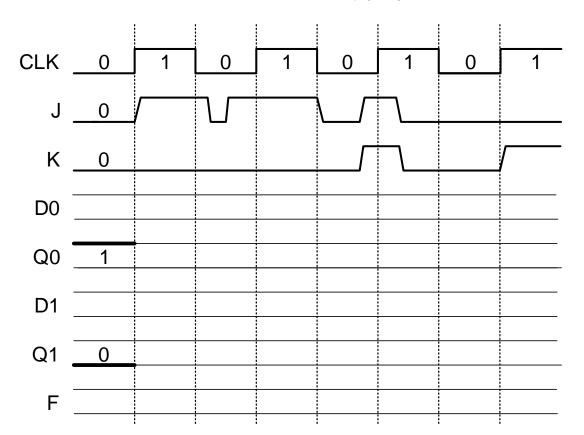

6. **Sequential Logic (12 pts.):** Complete the waveform for the operation of the circuit below. You need to know the behavior or logic of the full adder and we cannot answer questions about how that works. **The flip-flops are positive-edge triggered.**

We have added guide/grid lines for D0,Q0,D1,Q1, and F. You must draw the actual waveforms given the circuit above. We have started Q0 and Q1 by giving their initial values.

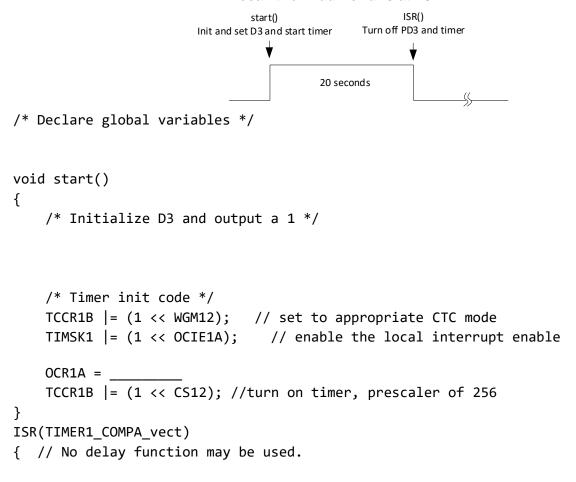

7. **Arduino Coding and Timers (10 pts)**: TIMER1 (16-bit timer) is to be used to generate one pulse of **20 seconds** on Port D, bit 3. When the "start" function is called, initialize bit D3 appropriately and start TIMER1. Some code is already provided. When the 20 seconds have elapsed, PD3 should go to zero and the timer should be stopped (should not run nor generate interrupts). You only need to generate one 20 second pulse and we do not want or need repeated 20-second pulses. **No delay functions are allowed**.

Assuming the prescaler is set to 256, a.) declare any needed global variables, b.) complete start() to initialize bit D3 and select a counter modulus, and c.) complete the ISR which should cause PD3 to be cleared to 0 after 20 second pulse as well as disabling the timer.

#### Recall the Arduino runs at 16 MHz.

## Intentionally blank for scratch work. You may detach it but please turn it in with your exam:

Name: \_\_\_\_\_\_ Section time: \_\_\_\_\_

| <u>(13)</u> | A   A - 1  | (13)  | $\Lambda \cdot \Lambda = 0$ | (Complement)    |

|-------------|------------|-------|-----------------------------|-----------------|

| (T5)        | X + X' = 1 | (T5') | $X \cdot X' = 0$            | (Complement)    |

| (T4)        | (X')' = X  |       |                             | (Involution)    |

| (T3)        | X + X = X  | (T3') | $X \bullet X = X$           | (Idempotency)   |

| ` /         |            | ( )   |                             |                 |

| (T2)        | X + 1 = 1  | (T2') | $X \bullet 0 = 0$           | (Null elements) |

| (T1)        | X + 0 = X  | (T1') | $X \cdot 1 = X$             | (Identities)    |

### Two- and Three-Variable Theorems

| 2 11 0 00100 | 210.00   00.0000 21000.0100                   |        |                                                     |                  |

|--------------|-----------------------------------------------|--------|-----------------------------------------------------|------------------|

| (T6)         | X + Y = Y + X                                 | (T6')  | $X \bullet Y = Y \bullet X$                         | (Commutativity)  |

| (T7)         | (X+Y)+Z=X+(Y+Z)                               | (T7')  | $(X \bullet Y) \bullet Z = X \bullet (Y \bullet Z)$ | (Associativity)  |

| (T8)         | $X \bullet (Y+Z) = X \bullet Y + X \bullet Z$ | (T8')  | $X+(Y \bullet Z) = (X+Y) \bullet (X+Z)$             | (Distributivity) |

| (T9)         | $X + X \bullet Y = X$                         | (T9')  | $X \bullet (X + Y) = X$                             | (Covering)       |

| (T10)        | $X \bullet Y + X \bullet Y' = X$              | (T10') | $(X+Y) \cdot (X+Y') = X$                            | (Combining)      |

| (T11)        | $X \bullet Y + X' \bullet Z + Y \bullet Z =$  | (T11') | $(X+Y) \bullet (X'+Z) \bullet (Y+Z) =$              | (Consensus)      |

|              | X•Y+X'Z                                       |        | $(X+Y)\bullet(X'+Z)$                                |                  |

|              |                                               |        |                                                     |                  |

#### DeMorgan's Theorem

| $(X \cdot Y)' = X' + Y' \qquad (X + Y)' = X' \cdot Y' \qquad (DeMorgan's)$ |

|----------------------------------------------------------------------------|

|----------------------------------------------------------------------------|